The 21 special function registers (26 in the 52 series) are discontinuously distributed in the 128-byte SFR storage space. The address space is 80H-FFH. In this SFR space, there are 128-bit address space, address It is also 80H-FFH, but there are only 83 effective bit addresses, which can perform bit addressing operations on some bits of 11 special function registers (here is a trick: all addresses that can be divisible by 8 can be bit addressable).

The descriptions are as follows:

1. ACC---is the accumulator, usually represented by A

What is this thing, but I can’t understand it from the name. It is a register, not an addition thing. Why is it given such a name? Perhaps it is because one of the numbers must be in ACC when the arithmetic unit is doing calculations. For the sake of it. It has a special name and a special identity. We will learn about instructions later in the second chapter, and we can find that all arithmetic instructions are inseparable from it. It has an all-zero mark Z, if A=0, then Z=1; if A≠0, then z=0. This flag is often used as a judgment condition for program branch transfer.

2. B-a register

When doing multiplication and division, put the multiplier or divisor, when not doing multiplication and division, use it as you like.

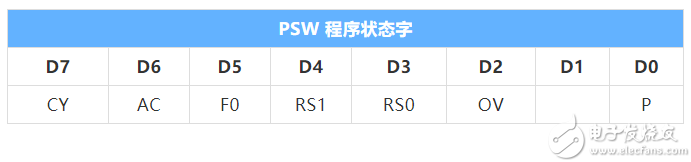

3. PSW-----program status word.

This is a very important thing. It contains many states of the CPU when it is working. With this, we can understand the current state of the CPU and make corresponding processing. Please see the table below for its functions:

Below we introduce each of your uses one by one

CY: Carry flag.

The arithmetic unit in the 8051 is an 8-bit arithmetic unit. We know that the 8-bit arithmetic unit can only represent 0-255. If you do addition, the addition of the two numbers may exceed 255, so the highest bit will be lost. What should I do if an operation error is caused? The highest bit is here. That's all right. With carry, borrow, CY=1; without carry, borrow, CY=0

Example: 78H+97H(01111000+10010111)

AC: Auxiliary advance and borrow (the advance and borrow between the upper nibble and the lower nibble).

Example: 57H+3AH(01010111+00111010)

F0: User flag

The user (programmer) decides when to use it and when not to use it.

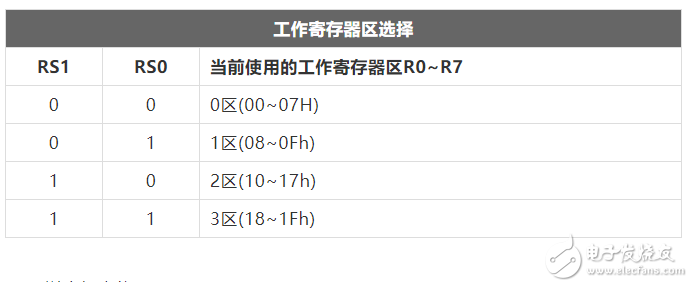

RS1, RS0: working register group selection bits

By modifying the status of the RS1 and RS0 bits in the PSW, a working register area can be selected. This feature improves the speed of MCS-51 field protection and field recovery. It is very beneficial to improve the working efficiency of the CPU and the speed of responding to interrupts. If in an actual application system, four groups of working registers are not needed, then the extra units in this area can be used as general data buffers.

0V: Overflow flag

The result of the calculation is understood by the complement calculation. With overflow, OV=1; without overflow, OV=0. What is overflow we will talk about in later chapters.

P: parity bit

It is used to express the parity of the number of binary digits "1" in the ALU operation result. If it is an odd number, then P=1, otherwise it is 0. The operation result has an odd number of 1, P=1; the operation result has an even number of 1, and P=0.

Example: The result of a certain operation is 78H (01111000), obviously the number of 1 is even, so P=0.

4. DPTR (DPH, DPL) -------- data pointer

It can be used to access any unit in the external data memory. If it is not used, it can also be used as a general-purpose register. It is up to us to decide how to use it. Divided into two registers, DPL (low 8 bits) and DPH (high 8 bits). Used to store 16-bit address value, in order to use indirect addressing or indexed addressing to perform data operations within 64K bytes of off-chip data RAM or program memory.

5. P0, P1, P2, P3--------input and output port (I/O) registers

We already know that this is the register of four parallel input/output ports (I/O). The content in it corresponds to the output of the pin.

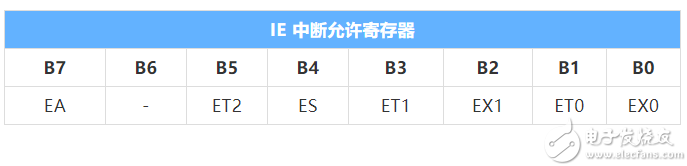

6. IE-----Interrupt Allowance Register

Bit addressable, address: A8H

â— EA (IE.7): when EA=0, all interrupts are disabled (that is, no interrupt is generated); when EA=1, the generation of each interrupt is determined by the individual enable bit

â—-(IE.6): reserved

â— ET2 (IE.5): Timer 2 overflow interrupt enable (for 8052)

â— ES (IE.4): Serial port interruption enabled (ES=1 enabled, ES=0 disabled)

â— ET1 (IE.3): Timing 1 interrupt allowed

â— EX1 (IE.2): External interrupt INT1 interrupt enable

â— ET0 (IE.1): Timer 0 interrupt enable

â— EX0 (IE.0): external interrupt INT0 interrupt enable

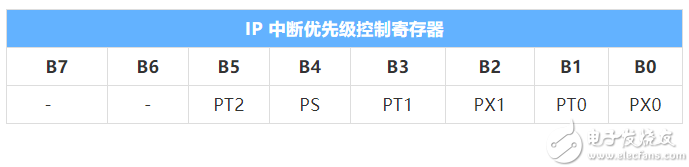

7. IP-----Interrupt Priority Control Register

Bit-addressable, address bit B8H

â—-(IP.7): reserved

â—-(IP.6): reserved

â— PT2 (IP.5): Timing 2 interrupt priority (for 8052)

â— PS (IP.4): Serial port interrupt priority

â— PT1 (IP.3): Timing 1 interrupt priority

â— PX1 (IP.2): External interrupt INT1 interrupt priority

â— PT0 (IP.1): Timer 0 interrupt priority

â— PX0 (IP.0): the interrupt priority of external interrupt INT0

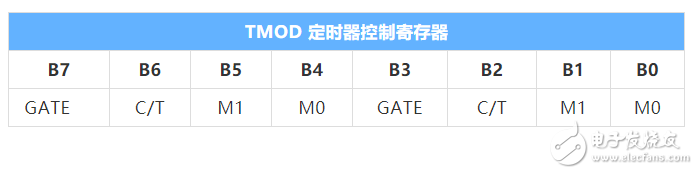

8. TMOD-----Timer control register

No bit-based addressing, address 89H

â— GATE: Timing operation switch control bit. When GATE=1, the INT0 or INT1 pin is high, and when the TR0 or TR1 control bit in TCON is 1, the timer/counter 0 or 1 starts to work. If GATE=0, as long as the TR0 or TR1 control bit is set to 1, the timer/counter 0 or 1 will start to work.

â— C/T: Select bit for timer or counter function. C/T=1 is a counter, input counting pulse through external pin T0 or T1. When C/T=0, it is a timer, and the internal system clock provides timing working pulses.

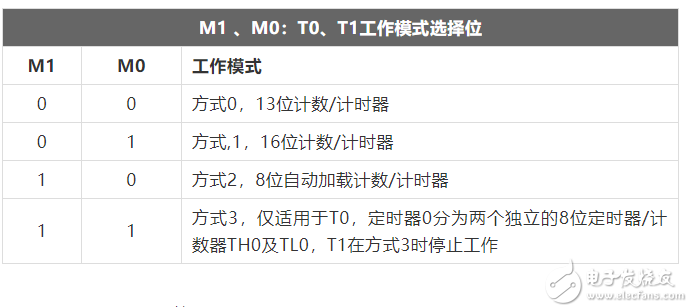

â— M1, M0: T0, T1 working mode selection bits

9. TCON-----Timer Control Register

Addressable by bit, address bit 88H

â— TF1: Timer T1 overflow flag, which can be queried and cleared by the program. TF1 is also the interrupt request source, which is cleared by hardware when the CPU responds to the T1 interrupt.

â— TF0: Timer T0 overflow flag, which can be queried and cleared by the program. TF0 is also the interrupt request source. It is cleared by hardware when the CPU responds to the T0 interrupt.

â— TR1: T1 count control bit, when it is 1, T1 count is enabled.

â— TR0: T0 charge count control bit, when it is 1, T0 count is allowed.

◠IE1: External interrupt 1 request source (INT1, P3.3) flag. IE1=1, external interrupt 1 is requesting an interrupt from the CPU. When the CPU responds to the interrupt, the hardware clears IE1 to “0†(edge ​​trigger mode).

â— IT1: External interrupt source 1 trigger mode control bit. IT1=0, external interrupt 1 program control is level trigger mode, when INT1 (P3.3) inputs low level, IE1 is set.

◠IE0: External interrupt 0 request source (INT0, P3.2) flag. IE0=1, external interrupt 1 is requesting an interrupt from the CPU. When the CPU responds to the interrupt, the hardware clears IE0 to “0†(edge-triggered mode).

â— IT0: External interrupt source 0 trigger mode control bit. IT0=0, external interrupt 1 program control is level trigger mode, when INT0 (P3.2) inputs low level, IE0 is set.

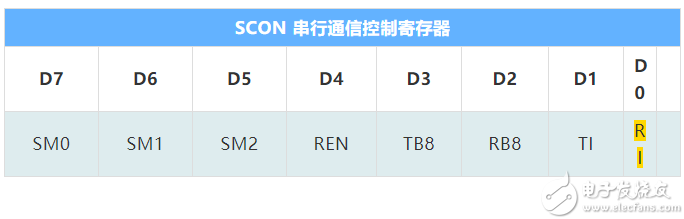

10. SCON----Serial communication control register

It is an addressable special register, used for serial data communication control, the unit address is 98H, and its structure format is as follows:

(1) SM0, SM1: serial port working mode control bits.

SM0, SM1 working mode

00 Mode 0-Baud rate is determined by the oscillator frequency: oscillator frequency/12

01 Mode 1-The baud rate is determined by the overflow rate of timer T1 or T2 and SMOD: 2SMOD × (T1 overflow rate)/32

10 Method 2-The baud rate is determined by the oscillator frequency and SMOD: 2SMOD × oscillator frequency/64

11 Mode 3-The baud rate is determined by the overflow rate of timer T1 or T2 and SMOD: 2SMOD × (T1 overflow rate)/32

(2) SM2: Multi-machine communication control bit. Multi-machine communication works in mode 2 and mode 3. The SM2 bit is mainly used in mode 2 and mode 3. In the receiving state, when the serial port works in mode 2 or 3, and SM2=1, only when the 9th bit of data (RB8) is 1 will the received first 8 bits of data be sent to SBUF and set Bit RI issues an interrupt request, otherwise the received data will be discarded. When SM2=0, no matter whether the first data is 0 or 1, it is rare that the data is sent to SBUF and an interrupt request is issued.

When working in mode 0, SM2 must be 0.

(3) REN: Allow to receive bit. REN is used to control the permission and prohibition of data reception. When REN=1, reception is allowed, and when REN=0, reception is prohibited.

(4) TB8: Send and receive data bit 8. In mode 2 and mode 3, TB8 is to be sent-the 9th data bit. In multi-machine communication, this bit must also be transmitted, and it represents the transmitted address or data. TB8=0 is data, and TB8=1 is address.

(5) RB8: Receive data bit 8.

In Mode 2 and Mode 3, RB8 stores the 9th bit of data received to identify the characteristics of the received data.

(6) TI: Send interrupt flag bit.

Addressable flag. In mode 0, after sending the 8th bit, it is set by hardware. In other modes, it is set by hardware before sending or stop bit. Therefore, TI=1 indicates the end of frame transmission, and TI can be cleared to “0†by software.

(7) RI: Receive interrupt flag bit.

Addressable flag. After receiving the 8th bit of data, this bit is set by hardware. In other working modes, this bit is set by hardware. RI=1 means the frame reception is completed.

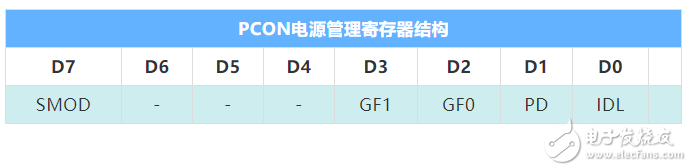

11. PCON-----Power Management Register

PCON is mainly a special register set up for the power control of CHMOS type single-chip microcomputer. The unit address is 87H, and its structure format is as follows:

In CHMOS-type single-chip microcomputers, except for the SMOD bit, the other bits are all dummy bits. SMOD is the serial port baud rate multiplication bit. When SMOD=1, the serial port baud rate is doubled. The system reset defaults to SMOD=0.

12. T2CON-----T2 status control register

â— TF2: T2 overflow interrupt flag. TF2 must be cleared to "0" by the user program. When T2 is used as a serial port baud rate generator, TF2 will not be set to "1".

â— EXF2: Timer T2 external interrupt flag. When EXEN2 is 1, the interrupt flag DXF2 is set when a negative transition occurs in T2EX (P1.1). EXF2 must be cleared to "0" by the user program.

â— TCLK: The transmission clock selection flag of the serial interface. When TCLK=1, T2 works in the baud rate generator mode.

â— RCLK: The receive clock selection flag of the serial interface. When RCLK=1, T2 works in baud rate generator mode.

â— EXEN2: External interrupt enable flag of T2.

â— C/T2: External counter/timer selection bit. When C/T2=1, T2 is an external event counter, and the counting pulse comes from T2 (P1.0); when C/T2=0, T2 is a timer, and the twelve frequency division signal of the oscillation pulse is used as the counting signal.

â— TR2: T2 count/timing control bit. When TR1 is 1, counting is allowed, and when TR1 is 0, counting is prohibited.

â— CP/RL2: Capture and constant automatic reload mode selection bit. When it is 1, it works in capture mode, and when it is 0, T2 works in constant automatic reloading mode. When TCLK or RCLK is 1, CP/RL2 is ignored, and T2 always works in constant automatic reloading mode.

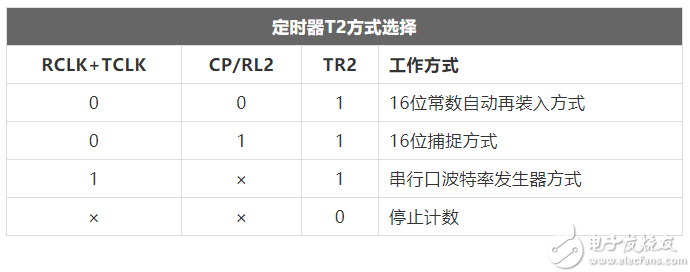

Below, the D0, D2, D4, and D5 bits of T2CON mainly control the working mode of T2, and the combined relationship of these bits is summarized below.

Solar Inverter,Frequency Inverter For Irrigation,Solar Inverter For Pumping System,3 Phase Solar Pump Inverter

Zhejiang Kaimin Electric Co., Ltd. , https://www.ckmineinverter.com