Network routers have statistical counters for performance monitoring, traffic management, network tracking, and network security. The counter is used to record the number of times a packet arrives and leaves and the number of specific events, such as when a bad packet occurs on the network. The arrival of a packet causes multiple different statistical counters to be updated; however, the number of statistical counters in a network device and its update rate are often limited by storage technology.

Managing statistical counters requires high performance memory to accommodate multiple read-modify-write operations. This article describes a unique statistical counter that uses the IP method. One end of the counter can be connected to a network processor (NPU) and the other end can be connected to a Xilinx QDR-IV memory controller. The QDR-IV Statistics Counter IP is a soft IP with QDR-IV SRAM that provides efficient statistical counters for network communication management and other counter applications.

Q DR-IV SRAM Overview

The QDR-IVSRAM is equipped with two bidirectional data ports A and B that can perform two data writes or two data read operations, or one read/write combination operation in one clock cycle. Therefore, this feature provides additional flexibility that architects can use in applications where read / write is not necessarily balanced. Each port can transmit data on both clock edges ( DDR (Double Data Rate) operation ), the operating mode is burst, and the burst length per clock cycle is two words ( each word is X18 or X36 ) . The address bus is general purpose, and its rising and falling edges provide addresses for Port A and Port B , respectively . Some manufacturers' QDR-IVSRAMs also support embedded ECC ( error checking and correction ) , which virtually eliminates soft errors and improves memory display reliability.

There are two types of QDR-IVSRAM: high performance (HP) QDR-IV and ultra high performance (XP) QDR-IV. HP devices have a maximum operating frequency of 667MHz, while XP devices have a maximum operating frequency of 1066 MHz. QDR-IV XP can increase performance by dividing the memory space into eight memory banks, represented by the three least significant bits (LSBs) of the address. The required storage scheme is to access different memory modules in the same cycle. From one cycle to another, all memory banks are accessible, and the system designer can allocate the memory address accordingly by planning the system architecture to take full advantage of the RTR performance of the Extreme Memory. This allows developers to dramatically increase performance while reducing overall system cost.

Statistics counter IP

The QDR IV Statistical Counter is a soft IP with QDR-IV SRAM and statistical counters for network communication management and other counter applications. The IP uses read-modify-write logic that supports the system management access port. One end of the IP can be connected to the network processing unit (NPU), and the other end can be connected to the QDR-IV storage controller. Since the statistic counter supports line cards at 400 Gbps and faster rates, performance is limited only by the FPGA and QDR-IV devices used.

Statistics counter IP operation

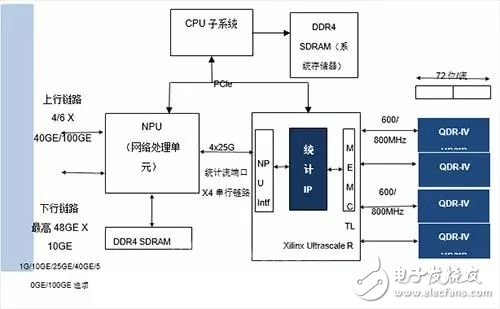

Figure 1 shows a use case for using QDR-IV and the statistical counter IP. A typical Network Processing Unit (NPU) sends a statistical (STATS) update request at a partner update rate of 800M per second . Each STATS request contains an entry/exit package command token with two counters (packets and byte counts) in a 72-bit word. The entire counter cache data is updated to a lifetime counter (usually DRAM) in system memory at 1 second intervals. This readback from the NPU is referred to as a processor (PROCS) update request. The PCIe interface is used to transmit counter cache data to update the lifetime counter. The figure below shows the setting of the STATS IP and the QDR-IV memory connected to the Xilinx memory controller, PCIe bus and NPU.

Figure 1 : Complete infrastructure with statistical IP , NPU, and memory

Statistical IP is available for HP and XP QDR-IV memories. Its mode of operation is controlled by a single parameter located at the top level interface of the IP design. Each stream address of two counters (packets and bytes) is a single 72-bit word. A 144Mb QDR-IV SRAM supports four million counters. The number of IP interfaces required for this design is comparable to the number of QDR-IV SRAMs used.

As shown in the block diagram, the NPU pushes statistics and processing requests to the IP over a 4x25 Gbps link. The IP operates at a frequency of one quarter of the memory access frequency and uses four parallel data paths called "channels" to match the memory bandwidth. In the storage interface HP and XP operating modes, port A acts as a read port and port B acts as a write port. Each statistical request performs a read-modify-write operation on counter data stored in a unique storage location associated with the request.

Read and write requests are delayed in a phased manner to match the QDR-IV memory read latency and memory controller latency. The phased design also serves as a service update request in the local cache cumulative latency process. In HP mode, there is no stats/processor update address limit through any of the four channels. The occurrence of an address may be random and there is no need to assign a specific type of address to each channel. However, since the block structure and restrictions of the memory are related to it in the XP mode, channels 0 and 1 are assigned to odd address locations that hold the ingress stream data, and channels 2 and 3 are assigned to even address locations that hold the egress stream data. This unique arrangement prevents block-limited locations that may occur in XP mode.

A one-second readback request from the processor is common in both modes of operation. The entire storage location needs to be read back in one second intervals, so the processor does not issue consecutive requests and is distributed at one second intervals. This activity resets the memory location each time a read request is requested by the processor.

Statistical IP architecture

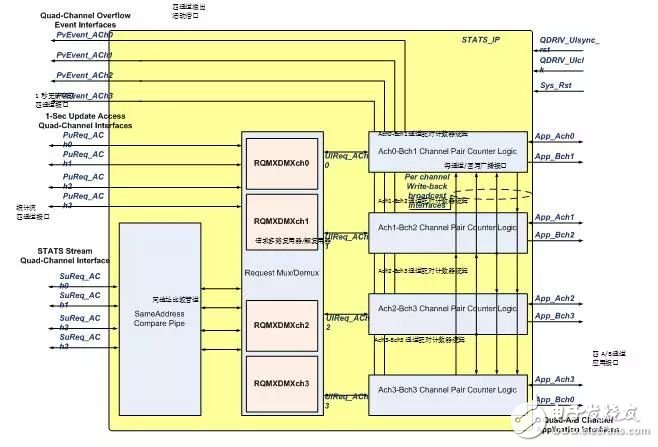

The STATS_IP architecture module in Figure 2 shows three subcomponents: the same address comparison pipeline ( SACOMP) block, the request-multiplex-demultiplex (REQ_MXDMX_CHn) block for each channel, and one QDR IV application channel per channel. 4 AB channel pair counter logic (ABCH_CTRL_CHn) block instances.

Figure 2: Statistical IP Architecture

The SACOMP block diagram contains two pipeline stages, one for compressing all four channels on the same clock cycle by comparison ( SACOMP_ChN-to-All ) and the other for bidirectional (burst) of the same address on a single channel 2 ) Compare ( SACOMP_B2BChN ) . When two or more channels are the same address in the specified time instance, the channel with the highest priority accumulates data appearing on the same address, and all other channels with lower priority and the same address will be invalid. This ensures that a single statistical request covers all channels with the same address, preventing any data consistency issues. The comparison and accumulation algorithms quickly assess all possible situations. In addition, on a single root channel, if there is a two-way statistical update request for the same storage location, the latest request fails and its data accumulates through the previously generated request. This ensures that bidirectional access to any of the same address locations does not occur in the read latency defined by the QDR-IV storage device.

The request-multiplex-demultiplex (RQMXDMXChn) block shown in FIG. 2 receives a processor update request and a statistical update request corresponding to the number of channels. Since the interval of the processor update request is fixed, RQMXDMXchN selects the processor request corresponding to the next clock service and stops the statistical request by the "request ready" backpressure signal. After processing each one-second update request, RQMXDMXchN stops configuring the processor request channel for the number of clocks (default is 10) to ensure that no consecutive one-second update request service is provided. The stop signal is sent to the NPU, ensuring that no new requests are generated until the backpressure signal fails. This mechanism can handle statistics and processor requests without blocking this design.

In the final phase, the AB channel pairing counter logic (ABCH_CTRLn) implements the actual read-modify-write mechanism for each statistical request while ensuring that each processor request is up-to-date. This phase includes read-delay pipeline logic, control multiplexing, read-write pipelines, and QDR-IV controller interface logic. The read and write latency pipeline takes into account memory and controller latency. Feedback mechanisms from adjacent channels and the same channel control multiplexing eliminate the possibility of all data consistency problems. The request flow in the pipeline initiates statistics and processor updates. The Control Multiplexing (CTRL_MUX) block distinguishes between the processor and the statistical request so that the current data can be forwarded as processor read data or pushed to the controller interface block for further processing. The controller interface block translates the actual read and write requests into controller-specific commands on port A and port B.

QDR-IV interface operation and application channel mapping

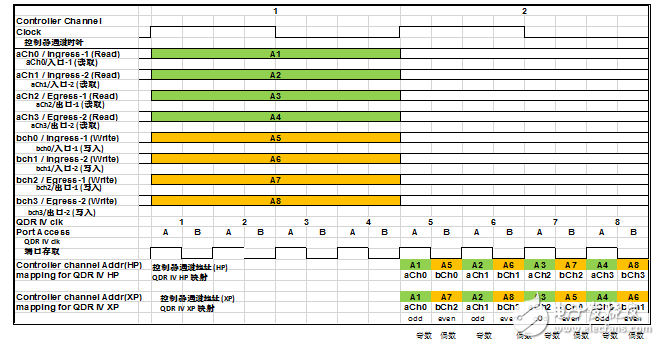

The statistical stream four channels and one second ( processor ) update the four channel interface as an application channel. The QDR IV controller uses 4:1/1:4 channel multiplexing / demultiplexing with a dedicated four-channel port interface defined for QDRIV Port A and Port B. The QDR-IV controller multiplexes and demultiplexes the channels in a fixed order , with the order between the application and the QDRIV device running at 4X clock frequency being ch0 , ch1 , ch2, and ch3 . Figure 3 shows the hypothetical QDR-IV controller sequence and recommended QDRIV HP statistical counter solution and QDRIV XP statistical counter solution application channel mapping.

image 3:

image 3:

QDR-IV interface 4:1/1:4 multiplexing/demultiplexing and application channel mapping

In the QDR-IVHP statistics counter, the requests for Port A and Port B are independent of the address and are arranged in the order of Ch0-Ch1-Ch2-Ch3 . This is because HP mode has no block requirements, and requests on port A and port B may contain addresses in the same location. However, in the QDR-IVXP statistics counter, the requests of port A and port B are arranged in the order of odd-even-odd-even, so that port A and port B do not appear to be the same in the same clock cycle. The address of the block.

Outdoor Mobile LED Kiosk Poster

The Best Advertising choice and the best money earning machine--Outdoor LED screen kiosk

Outdoor Led Kiosk Poster also called led AD Kiosk player is one of new applications for led displays. Developed from led screens, it is more suitable and friendly to operate. Don't need to install as it is floor standing. and could be put anywhere it needed indoor or outdoor environment.

Optional Pixel Pitch 4mm,5mm,6mm.optional sizes 60`'.IP65/54, weather proof; Ultra Outdoor HD led display Kiosk poster, crystal clear and vivid images; High brightness and auto adjustment according to environment; Intelligent group management, easy and convenient. Thanks to the Cluster controll system and GPS technology, no matter how many posters you have where they are, you could controll them easily and change content quickly.

They are one of none stop money earning machines!

Intelligent monitoring and GPS

High brightness for outdoor and energy saving

Outdoor Mobile Led Poster,Mobile Led Poster,Outdoor Display Of Mobile Led Poster,Led Screen Of Window Signage

Shenzhen Priva Tech Co., Ltd. , https://www.privaled.com